FPGA面试真题解析_fpga二进制编码为啥用较多组合逻辑-程序员宅基地

FPGA面试真题解析

1、1、 十进制46.25对应的二进制表达式为( )。(硬件逻辑实习岗)

A 101110.11 B 101101.01 C 101110.1 D 101110.01

解析:

这个问题看上去很简单,那是因为我们平时可以打开电脑上的计算器,然后用程

序员功能立刻就能出结果,但是笔试的时候我们并不能使用这种“作弊“的功能,所以还是要会手算。可能很多同学数电是大一大二时学习的,很久没有接触过这么基础的问题了,那就让我们一起来回忆下吧。

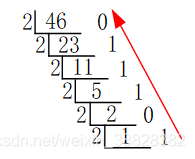

首先这个题目是由整数部分和小数不同共同组成的,整数部分的计算是最简单的,整数部分除以2得到的余数按照逆向顺序排列后就是整数部分转化为二进制后的结果,详细过程如下所示:

46转化为二进制的结果就是101110

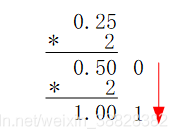

小数部分的计算可能很多人记不清楚了,小数部分每次乘以2后得出的结果取其整数部分,直到小数部分为0或达到精度要求为止,详细过程如下所示:

0.25转化为二进制的结果就是.01

综上所述,最后的答案选择D 101110.01

2、2、 在时序电路的状态转换表中,若状态数N=3,则状态变量数最少为( ) (硬件逻辑实习岗)

A 4 B 8 C 2 D 16

解析:

让我们先看一下一个完整的状态机代码都有哪些内容

//---------------------------------

01 module simple_fsm(

02 input wire sys_clk , //系统时钟50Mh

03 input wire sys_rst_n , //全局复位

04 input wire pi_money , //投币方式可以为:不投币(0)、投1元(1)

05

06 output reg po_cola //po_colaΪ1ʱ֣po_colaΪ0ʱ֠

07 );

08

09 //只有三种状态,使用独热码

10 parameter IDLE = 3’b001;

11 parameter ONE = 3’b010;

12 parameter TWO = 3’b100;

13

14 reg [2:0] state;

15

16 //第一段状态机,描述state跳转,用case

17 always@(posedge sys_clk or negedge sys_rst_n)

18 if(sys_rst_n == 1’b0)

19 state <= IDLE;

20 else case(state)

21 IDLE : if(pi_money == 1’b1) //判断输入情况

22 state <= ONE;

23 else

24 state <= IDLE;

25

26 ONE : if(pi_money == 1’b1)

27 state <= TWO;

28 else

29 state <= ONE;

30

31 TWO : if(pi_money == 1’b1)

32 state <= IDLE;

33 else

34 state <= TWO;

35

36 default : state <= IDLE;

37 endcase

38

39 //第二段状态机,描述state如何影响po_cola输出

40 always@(posedge sys_clk or negedge sys_rst_n)

41 if(sys_rst_n == 1’b0)

42 po_cola <= 1’b0;

43 else if((state == TWO) && (pi_money == 1’b1))

44 po_cola <= 1’b1;

45 else

46 po_cola <= 1’b0;

47

48 endmodule

//---------------------------------

上面是一个用Verilog描述的简单状态机,其功能是每次只能输入1元硬币,输入3元时出可乐,其中01-07行是端口列表部分,10-12行是状态编码部分,14行是定义的状态变量,17-37行是第一段状态机部分,40-46是第二段状态机部分。

题目中说状态数有3个,状态变量数最少为多少(此处应该是指位宽)?上面的例子中10-12行是状态编码,即有多少个状态数就需要有多少个状态编码,这里一共有3种;14行是状态变量,这里为什么状态变量的位宽是3呢?因为我们采用了独热码的编码方式,每个状态数只有1比特为1,其余比特都为0,所以3个状态就要用3位宽的变量,如果是4个状态那就要用4位宽的变量,也就是一共有几个状态数就需要几位宽的状态变量。而题目中说的是“最少“,那么除了我们用独热码的方式对状态进行编码,还有其他的方法吗?答案是当然。我们还可以采用二进制码或格雷码的方式对状态进行编码,上面的例子中如果我们用二进制码编码3个状态则为:2‘b00,2‘b01,2‘b10;而用格雷码编码3个状态则为:2‘b00,2‘b01,2‘b11,都只需要2位宽的状态变量即可,即便是有4个状态数,我们使用2位宽的状态变量依然可以解决问题,要比独热码更节省状态变量的位宽个数。所以这里答案选择C 2。

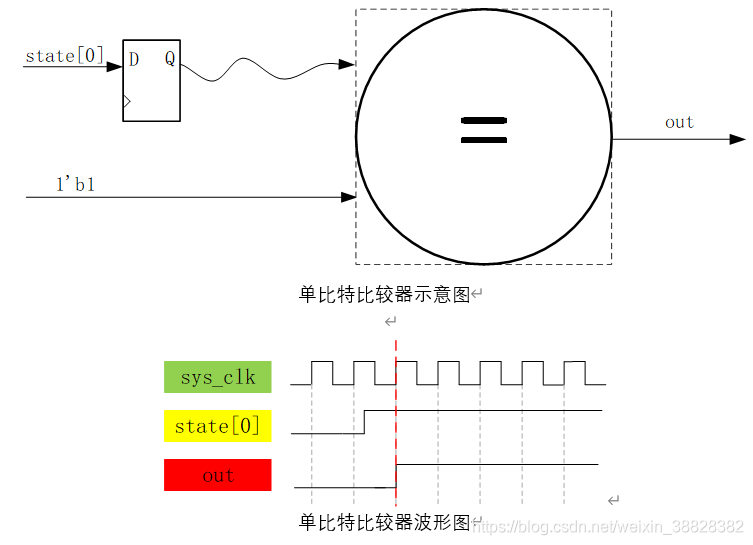

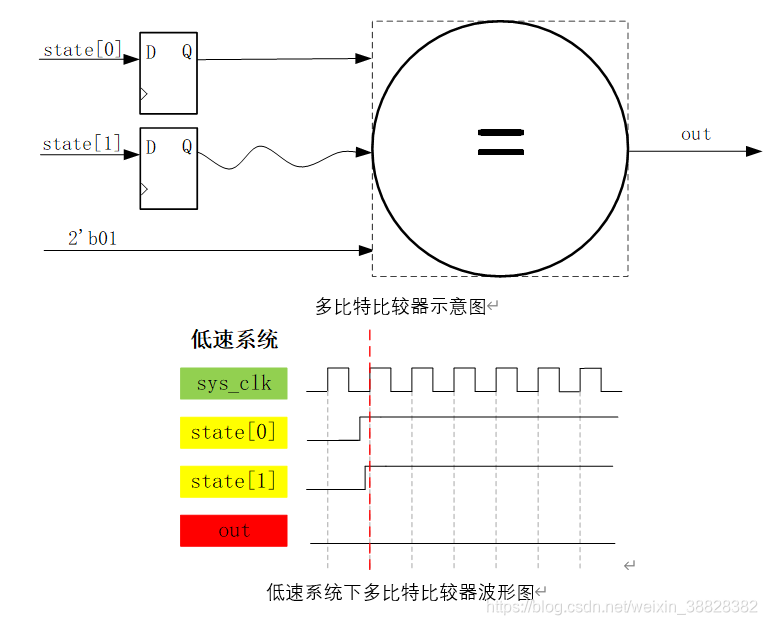

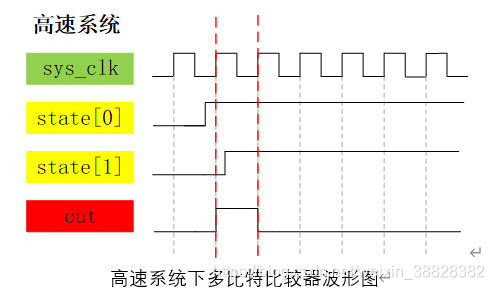

讲到这里并没有结束,我们稍微拓展一下让大家学到更多。为什么例子中我们使用的是独热码而非二进制码或格雷码呢?那就要从每种编码的特性上说起了,首先独热码因为每个状态只有1bit是不同的,所以在执行到43行时的(state == TWO)这条语句时,综合器会识别出这是一个比较器,而因为只有1比特为1,所以综合器会进行智能优化为(state[2] == 1’b1),这就相当于把之前3比特的比较器变为了1比特的比较器,大大节省了组合逻辑资源,但是付出的代价就是状态变量的位宽需要的比较多,而我们FPGA中组合逻辑资源相对较少,所以比较宝贵,而寄存器资源较多,所以很完美。而二进制编码的情况和独热码刚好相反,他因为使用了较少的状态变量,使之在减少了寄存器状态的同时无法进行比较器部分的优化,所以使用的寄存器资源较少,而使用的组合逻辑资源较多,我们还知道CPLD就是一个组合逻辑资源多而寄存器逻辑资源少的器件,因为这里我们使用的是FPGA器件,所以使用独热码进行编码。就因为这个比较部分的优化,还使得使用独热码编码的状态机可以在高速系统上运行,其原因是多比特的比较器每个比特到达比较器的时间可能会因为布局布线的走线长短而导致路径延时的不同,这样在高速系统下,就会导致采集到不稳定的状态,导致比较后的结果产生一个时钟的毛刺,使输出不稳定,而单比特的比较器就不用考虑这种问题。下面是示意图解析。

用独热码编码虽然好处多多,但是如果状态数非常多的话即使是FPGA也吃不消独热码对寄存器的消耗,所以当状态数特别多的时候可以使用格雷码对状态进行编码。格雷码虽然也是和二进制编码一样使用的寄存器资源少,组合逻辑资源多,但是其相邻状态转换时只有一个状态发生翻转,这样不仅能消除状态转换时由多条信号线的传输延迟所造成的毛刺,又可以降低功耗,所以要优于二进制编码的方式,相当于是独热码和二进制编码的折中。

最后我们用一个表格来总结一下什么时候使用什么方式的编码效果最好 (有时候不管你使用哪种编码方式,综合器会根据实际情况在综合时智能的给你进行编码的转换,当然这需要你设置额外的综合约束,这里我们不再详细讲解) 。

3、3、 只读存储器ROM中的内容,当电源断掉后又接通,存储器中的内容 ( )。(硬件逻辑实习岗)

A 全部为0 B不可预料 C 保持不变 D 全部改变

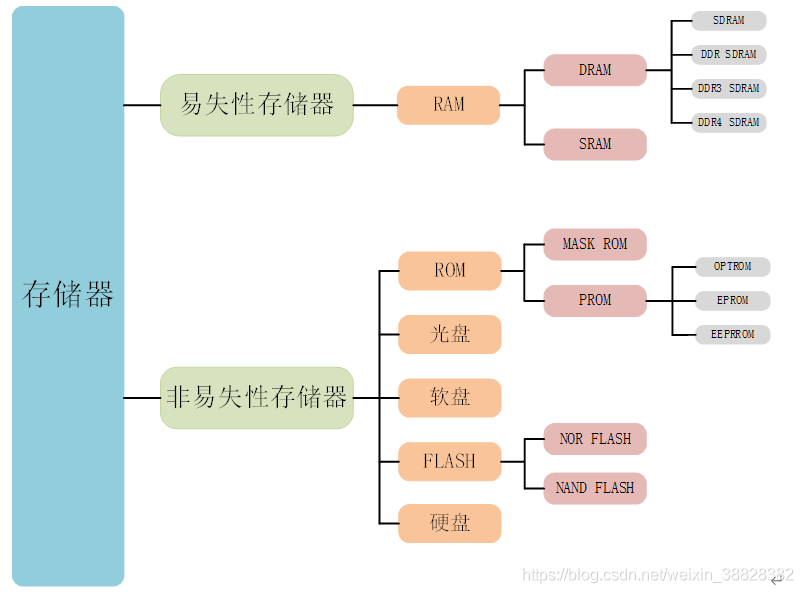

解析:考察数字电路中存储器的基本知识

下图所示为常见存储器件的性质关系

一、易失性存储器的代表就是RAM,RAM又分为DRAM(动态随机存储器)和SRAM(静态随机存储器),它们之间主要在于生产工艺不同。

SRAM保存数据是通过晶体管进行锁存的,其工艺复杂,生产成本高,所以价格相对较贵,不易做大容量,但是速度更快;DRAM保存数据靠电容充电来维持容量,生产成本较SRAM低,所以价格相对便宜,容量可以做到很大,速度虽然不如SRAM快但是随着工艺技术的提升,速度也很可观,所以较为常用。DRAM和SRAM都是异步通信的,速率没有SDRAM(同步动态随机存储器)和SSRAM(同步静态随机存储器)快。所以现在大容量RAM存储器是选用SDRAM的。

CPU中的Cache实质属于SRAM,而内存条则是属于DRAM。SDRAM和DDR SDRAM的区别在于DDR(Double Data Rate)是双倍速率。SDRAM只在时钟的上升沿表示一个数据,而DDR SDRAM能在上升沿和下降沿都表示一个数据。DDR也一步步经过改良出现了一代、二代、三代、四代,以及低功耗版本,现在也有五代。

二、 非易失性存储器常见的有ROM,FLASH,光盘,软盘,硬盘。他们作用相同,只是实现工艺不一样。

ROM(Read Only Memory)在以前就是只读存储器,就是说这种存储器只能读取它里面的数据无法向里面写数据。实际是以前向存储器写数据不容易,所以这种存储器就是厂家造好了写入数据,后面不能再次修改。现在技术成熟了,ROM也可以写数据,但是名字保留了下来。ROM分为MASK ROM、OTPROM、EPROM、EEPROM。MASK ROM是掩膜ROM这种ROM是一旦厂家生产出来,使用者无法再更改里面的数据。OTPROM(One Time Programable ROM)一次可变成存储器,出厂后用户只能写一次数据,然后再也不能修改了,一般做存储密钥。EPROM(Easerable Programable ROM)这种存储器就可以多次擦除然后多次写入了。但是要在特定环境紫外线下擦除,所以这种存储器也不方便写入。EEPROM(Eelectrically Easerable Programable ROM)电可擦除ROM,现在使用的比较多因为只要有电就可擦除数据,就可以写入数据。

FLASH是一种可以写入和读取的存储器,叫闪存,FLASH也叫FLASH ROM,有人把FLASH当做ROM。FLASH和EEPROM相比,FLASH的存储容量大。FLASH的速度比现在的机械硬盘速度快,现在的U盘和SSD固态硬盘都是Nandflash。FLASH又分为Norflash和Nandflash。

综上所述,本题答案选C 保持不变

4、4、 在Verilog语言中,a = 4’b1011,那么&a为( )。(硬件逻辑实习岗)

A 4’b1111 B 1’b1 C 1’b0 D 4’b1011

解析:考察Verilog基本语法中的操作符

“&”操作符有两种用途,既可以作为一元操作符(仅有一个操作数),也可以作为二元操作符(有两个操作数)。

当“&”作为一元操作符时表示归约与。&m是将m中所有比特相与,最后的结果为1bit。例:&4‘b1111 = 1&1&1&1 = 1’b1,&4’b1101 = 1&1&0&1 = 1’b0。

当“&”作为二元操作符时表示按位与。m&n是将m的每个比特与n的相应比特相与,在运算的时候要保证m和n的比特数相等,最后的结果和m(n)的比特数相同。例:4’b1010&4’b0101 = 4’b0000,4’b1101&4’b1111 = 4’b1101。

我们在写Verilog代码时常常当if的条件有多个同时满足时就执行使用“&&”逻辑与操作符。m &&n是判断m和n是否都为真,最后的结果只有1bit,如果都为真则输出1‘b1,如果不都为真则输出1’b0。要注意和“&”的功能区分。

此外“&”操作符作为归约与使用时还有妙用。下面是一个分频器,代码结构简单,逻辑也不复杂,就是当计数器计数到15时让输出out取反,相当于实现对sclk的32分频。

//---------------------------------

01 module divider(

02 input wire sclk ,

03 input wire rst_n ,

04

05 output reg out

06 );

07

08 reg [3:0] cnt;

09

10 //cnt

11 always@(posedge sclk or negedge rst_n)

12 if(rst_n == 1’b0)

13 cnt <= 4’b0;

14 else if(cnt == 4’d15)

15 cnt <= 4’b0;

16 else

17 cnt <= cnt + 1’b1;

18

19 //out

20 always@(posedge sclk or negedge rst_n)

21 if(rst_n == 1’b0)

22 out <= 1’b0;

23 else if(cnt == 4’d15)

24 out <= ~out;

25

26 endmodule

//---------------------------------

我们可以看到第14行和低23行都使用了一个判断语句,是判断计数器cnt是否达到15,如果达到是计数器清零,且输出out取反。我们比较器要将cnt的每一个比特都和4‘d15的每一位进行比较,也就是判断(cnt == 4’b1111),会浪费更多的资源。而我们今天想到了“&”的用法就可以实现妙用,我们将判断条件改为(&cnt == 1‘b1),当计数器计数到15时,即所有的比特都为变为了1,那么&cnt为1‘b1,而其余情况&cnt都为1’b0,这样比较的位数就只有1位了,节省了资源。希望大家以后遇到此类相关情况推荐使用“&cnt”的方法。

注:如果大家在使用QuartusII工具进行验证上面的结论,想看看是否真的会节约逻辑资源时,可能看不到想要的结果,这是因为当描述的系统不复杂时综合器能够比较好的对逻辑进行优化(证明被优化的结果可以通过RTL视图定位在Chip Planner中的位置得到验证),而当描述的系统较为复杂时就不能够保证综合器能够有比较好的优化效果,或许以后综合器可以变得更加智能,但是目前还是使用推荐的写法更稳妥。

综上所述,本题答案选C 1‘b0

智能推荐

攻防世界_难度8_happy_puzzle_攻防世界困难模式攻略图文-程序员宅基地

文章浏览阅读645次。这个肯定是末尾的IDAT了,因为IDAT必须要满了才会开始一下个IDAT,这个明显就是末尾的IDAT了。,对应下面的create_head()代码。,对应下面的create_tail()代码。不要考虑爆破,我已经试了一下,太多情况了。题目来源:UNCTF。_攻防世界困难模式攻略图文

达梦数据库的导出(备份)、导入_达梦数据库导入导出-程序员宅基地

文章浏览阅读2.9k次,点赞3次,收藏10次。偶尔会用到,记录、分享。1. 数据库导出1.1 切换到dmdba用户su - dmdba1.2 进入达梦数据库安装路径的bin目录,执行导库操作 导出语句:./dexp cwy_init/[email protected]:5236 file=cwy_init.dmp log=cwy_init_exp.log 注释: cwy_init/init_123..._达梦数据库导入导出

js引入kindeditor富文本编辑器的使用_kindeditor.js-程序员宅基地

文章浏览阅读1.9k次。1. 在官网上下载KindEditor文件,可以删掉不需要要到的jsp,asp,asp.net和php文件夹。接着把文件夹放到项目文件目录下。2. 修改html文件,在页面引入js文件:<script type="text/javascript" src="./kindeditor/kindeditor-all.js"></script><script type="text/javascript" src="./kindeditor/lang/zh-CN.js"_kindeditor.js

STM32学习过程记录11——基于STM32G431CBU6硬件SPI+DMA的高效WS2812B控制方法-程序员宅基地

文章浏览阅读2.3k次,点赞6次,收藏14次。SPI的详情简介不必赘述。假设我们通过SPI发送0xAA,我们的数据线就会变为10101010,通过修改不同的内容,即可修改SPI中0和1的持续时间。比如0xF0即为前半周期为高电平,后半周期为低电平的状态。在SPI的通信模式中,CPHA配置会影响该实验,下图展示了不同采样位置的SPI时序图[1]。CPOL = 0,CPHA = 1:CLK空闲状态 = 低电平,数据在下降沿采样,并在上升沿移出CPOL = 0,CPHA = 0:CLK空闲状态 = 低电平,数据在上升沿采样,并在下降沿移出。_stm32g431cbu6

计算机网络-数据链路层_接收方收到链路层数据后,使用crc检验后,余数为0,说明链路层的传输时可靠传输-程序员宅基地

文章浏览阅读1.2k次,点赞2次,收藏8次。数据链路层习题自测问题1.数据链路(即逻辑链路)与链路(即物理链路)有何区别?“电路接通了”与”数据链路接通了”的区别何在?2.数据链路层中的链路控制包括哪些功能?试讨论数据链路层做成可靠的链路层有哪些优点和缺点。3.网络适配器的作用是什么?网络适配器工作在哪一层?4.数据链路层的三个基本问题(帧定界、透明传输和差错检测)为什么都必须加以解决?5.如果在数据链路层不进行帧定界,会发生什么问题?6.PPP协议的主要特点是什么?为什么PPP不使用帧的编号?PPP适用于什么情况?为什么PPP协议不_接收方收到链路层数据后,使用crc检验后,余数为0,说明链路层的传输时可靠传输

软件测试工程师移民加拿大_无证移民,未受过软件工程师的教育(第1部分)-程序员宅基地

文章浏览阅读587次。软件测试工程师移民加拿大 无证移民,未受过软件工程师的教育(第1部分) (Undocumented Immigrant With No Education to Software Engineer(Part 1))Before I start, I want you to please bear with me on the way I write, I have very little gen...

随便推点

Thinkpad X250 secure boot failed 启动失败问题解决_安装完系统提示secureboot failure-程序员宅基地

文章浏览阅读304次。Thinkpad X250笔记本电脑,装的是FreeBSD,进入BIOS修改虚拟化配置(其后可能是误设置了安全开机),保存退出后系统无法启动,显示:secure boot failed ,把自己惊出一身冷汗,因为这台笔记本刚好还没开始做备份.....根据错误提示,到bios里面去找相关配置,在Security里面找到了Secure Boot选项,发现果然被设置为Enabled,将其修改为Disabled ,再开机,终于正常启动了。_安装完系统提示secureboot failure

C++如何做字符串分割(5种方法)_c++ 字符串分割-程序员宅基地

文章浏览阅读10w+次,点赞93次,收藏352次。1、用strtok函数进行字符串分割原型: char *strtok(char *str, const char *delim);功能:分解字符串为一组字符串。参数说明:str为要分解的字符串,delim为分隔符字符串。返回值:从str开头开始的一个个被分割的串。当没有被分割的串时则返回NULL。其它:strtok函数线程不安全,可以使用strtok_r替代。示例://借助strtok实现split#include <string.h>#include <stdio.h&_c++ 字符串分割

2013第四届蓝桥杯 C/C++本科A组 真题答案解析_2013年第四届c a组蓝桥杯省赛真题解答-程序员宅基地

文章浏览阅读2.3k次。1 .高斯日记 大数学家高斯有个好习惯:无论如何都要记日记。他的日记有个与众不同的地方,他从不注明年月日,而是用一个整数代替,比如:4210后来人们知道,那个整数就是日期,它表示那一天是高斯出生后的第几天。这或许也是个好习惯,它时时刻刻提醒着主人:日子又过去一天,还有多少时光可以用于浪费呢?高斯出生于:1777年4月30日。在高斯发现的一个重要定理的日记_2013年第四届c a组蓝桥杯省赛真题解答

基于供需算法优化的核极限学习机(KELM)分类算法-程序员宅基地

文章浏览阅读851次,点赞17次,收藏22次。摘要:本文利用供需算法对核极限学习机(KELM)进行优化,并用于分类。

metasploitable2渗透测试_metasploitable2怎么进入-程序员宅基地

文章浏览阅读1.1k次。一、系统弱密码登录1、在kali上执行命令行telnet 192.168.26.1292、Login和password都输入msfadmin3、登录成功,进入系统4、测试如下:二、MySQL弱密码登录:1、在kali上执行mysql –h 192.168.26.129 –u root2、登录成功,进入MySQL系统3、测试效果:三、PostgreSQL弱密码登录1、在Kali上执行psql -h 192.168.26.129 –U post..._metasploitable2怎么进入

Python学习之路:从入门到精通的指南_python人工智能开发从入门到精通pdf-程序员宅基地

文章浏览阅读257次。本文将为初学者提供Python学习的详细指南,从Python的历史、基础语法和数据类型到面向对象编程、模块和库的使用。通过本文,您将能够掌握Python编程的核心概念,为今后的编程学习和实践打下坚实基础。_python人工智能开发从入门到精通pdf