VerilogHDL可综合描述原则,常用语法描述对应的硬件结构

”VerilogHDL可综合描述原“ 的搜索结果

在开篇的时候,我先讲一下IC设计分类跟设计流程,提前声明一下,由于本人水平有限,加上没有完全亲身体验过从设计规划到工艺制造这一完整的设计流程,只是知道这一流程的某些步骤,因此本篇的设计流程是我根据我的...

Verilog学习、调测试记录

FPGA基础语法

关注、星标嵌入式客栈,精彩及时送达[导读] 基于FPGA的SOC在嵌入式系统应用越来越广了,往往一个复杂系统使用一个单芯片基于FPGA的SOC就搞定了。比较流行的方案主要有Altera/...

Verilog作为一种HDL,硬件描述语言,是如何在不同的抽象层级上描述电路的?描述电路的方式有哪些?

对于assign关键字描述的组合逻辑 (通常为连续赋值语句) ,统一使用 “=” ,变量定义为 wire 型变量 注:在后两项中使用 “=” 主要原因在于避免产生组合逻辑环, 其会导致在时序路径无法被工具分析从而使不同批次器件...

用 Verilog HDL 来描述加法器是相当容易的,只需要把运算表达式写出就可以了,见下例。 module add_4( X, Y, sum, C); input [3 : 0] X, Y; output [3: 0] sum; output C; assign {C, Sum } = X + Y; endmodule...

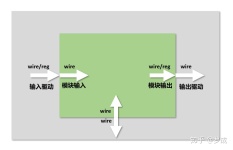

Verilog程序的基本设计单元是“模块”,模块完全定义在module 和endmodule关键字之间。 每个模块包含四个主要部分:模块声明,端口定义,数据类型说明和 逻辑功能描述。 module <模块名> ( <端口> ...

阻塞和非阻塞赋值的语言结构是Verilog 语言中最难理解概念之一。甚至有些很有经验的Verilog 设计工程师也不能完全正确地理解:何时使用非阻塞赋值,何时使用阻塞赋值才能设计出符合要求的电路。

FPGA比较擅长的是作定点数整数运算,那么对于带有小数部分的乘加运算。一般都选择先扩大若干倍,而后将运算结果缩小若干倍实现。

Verilog HDL 入门到精通

由于想学习FPGA的相关内容,同时给数字电路打点基础,于是借助着B站上西安电子科技大学的视频开始学习Verilog HDL这门硬件描述语言,在学完语言后,将按照**《FPGA设计技巧与案例开发详解》**这本书上的相关内容在一...

北航计算机学院-计算机组成原理课程设计-2020秋,PreProject-Verilog HDL与ISE-前言。 北航计算机学院的计算机组成原理课程设计,是高度实践性的专业课程,一共会有P0~P9九个project,以及进入project之前的预备知识...

用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型。Verilog HDL既是一种行为描述的语言也是一种结构描述的语言。这也就是说,既可以用电路的功能描述也可以用元器件和它们之间的连接来建立所设计电路的...

verilog HDL总结 (2010-09-16 16:38:12)转载▼标签: 杂谈 分类: EDA1. Assign 语句中赋值的变量不能定义为reg型。2 Always块里面写的是触发信息。3 测试模块里要包含所有的情况。如果可以先把波形图画出来,再按照...

1.数字电路基础知识: 布尔代数、门级电路的内部晶体管结构、组合逻辑电路分析与设计、触发器、时序逻辑电路分析与设计 2.数字系统的构成: 传感器AD数字处理器DA执行部件 3.程序通在硬件上的执行过程:C语言(经过...

一、HDL的概念和特征 HDL,Hard Discrimination Language的缩写,翻译过来就是硬件描述语言。那么什么是硬件描述语言呢?为什么不叫硬件设计语言呢?硬件描述语言,顾名思义就是描述硬件的语言,它用文本的形式来...

用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型。Verilog HDL既是一种行为描述的语言也是一种结构描述的语言。这也就是说,既可以用电路的功能描述也可以用元器件和它们之间的连接来建立所设计电路的...

推荐文章

- Unity3D 导入资源_unity怎么导入压缩包-程序员宅基地

- jqgrid 服务器端验证,javascript – jqgrid服务器端错误消息/验证处理-程序员宅基地

- 白山头讲PV: 用calibre进行layout之间的比对-程序员宅基地

- java exit方法_Java:如何测试调用System.exit()的方法?-程序员宅基地

- 如何在金山云上部署高可用Oracle数据库服务_rman target sys/holyp#ssw0rd2024@gdcamspri auxilia-程序员宅基地

- Spring整合Activemq-程序员宅基地

- 语义分割入门的总结-程序员宅基地

- SpringBoot实践(三十五):JVM信息分析_怎样查看springboot项目的jvm状态-程序员宅基地

- 基于springboot+vue的戒毒所人员管理系统 毕业设计-附源码251514_戒毒所管理系统-程序员宅基地

- 【LeetCode】面试题57 - II. 和为s的连续正数序列_leet code 和为s的正数序列 java-程序员宅基地